作者: 深圳市昂洋科技有限公司發(fā)表時間:2025-07-02 14:29:13瀏覽量:19【小中大】

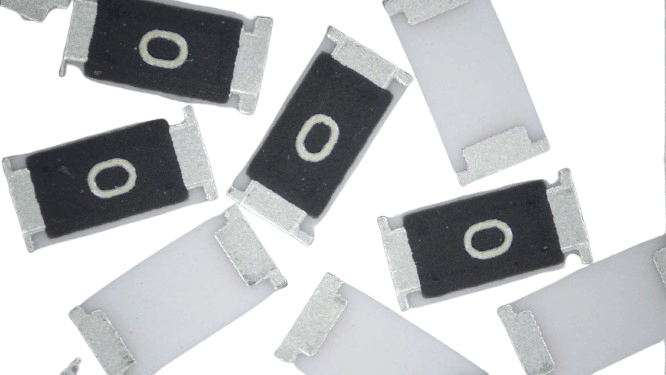

在電子元件制造領(lǐng)域,厚聲貼片電阻憑借其小型化、高可靠性的特點,成為消費電子、汽車電子等領(lǐng)域的核心元件。其制造工藝主要分為厚膜與薄膜兩大技術(shù)路線,二者在材料、工藝、性能及應(yīng)用場景上存在顯著差異。

工藝原理:物理沉積與化學(xué)燒結(jié)的分野

厚膜工藝采用絲網(wǎng)印刷技術(shù),將電阻漿料(含金屬氧化物、玻璃粘結(jié)相及有機載體)通過絲網(wǎng)漏印至陶瓷基板,經(jīng)800-900℃高溫?zé)Y(jié)形成電阻體。該工藝中,電阻膜厚度通常達10-50微米,其核心在于通過漿料配方調(diào)整實現(xiàn)阻值控制,例如增加金屬氧化物比例可降低電阻率。

典型應(yīng)用如厚聲RC系列電阻,通過氧化鋁基板與鈀銀電極的組合,實現(xiàn)低成本大規(guī)模生產(chǎn)。

薄膜工藝則依托真空鍍膜技術(shù),在氧化鋁陶瓷基板上通過磁控濺射沉積鎳鉻合金薄膜,厚度僅0.1-1微米。隨后采用光刻工藝對薄膜進行圖形化蝕刻,形成精確電阻體。以風(fēng)華高科薄膜電阻為例,其通過激光調(diào)阻技術(shù)可將阻值精度控制在±0.01%,溫度系數(shù)低至±5PPM/℃,滿足醫(yī)療設(shè)備等高精度場景需求。

性能對比:精度與穩(wěn)定性的博弈

厚膜電阻因漿料燒結(jié)特性,存在天然的阻值離散性,常見精度為±1%、±5%,溫度系數(shù)達±200PPM/℃。但其結(jié)構(gòu)優(yōu)勢顯著:厚膜層與陶瓷基板的結(jié)合強度高,耐脈沖能力突出,可承受1000次以上浪涌沖擊。此外,厚膜工藝支持大功率設(shè)計,如厚聲2512封裝電阻額定功率達1W,適用于電源模塊等高能耗場景。

薄膜電阻則通過納米級薄膜的均勻沉積實現(xiàn)超高精度,其溫度系數(shù)可控制在±10PPM/℃以內(nèi),阻值長期穩(wěn)定性優(yōu)于0.1%。以村田薄膜電阻為例,其采用TaN(氮化鉭)材料,在-55℃至155℃溫域內(nèi)阻值漂移小于0.05%,成為5G基站、精密儀器等領(lǐng)域的首選。

應(yīng)用場景:成本與性能的平衡術(shù)

厚膜工藝憑借成本優(yōu)勢占據(jù)主流市場,其產(chǎn)品單價較薄膜電阻低40%-60%,廣泛應(yīng)用于對精度要求不高的消費電子領(lǐng)域。例如,厚聲0402封裝厚膜電阻在智能手機中用量超百顆,主要用于電源濾波、信號分壓等基礎(chǔ)電路。

薄膜電阻則聚焦高端市場,在醫(yī)療影像設(shè)備中,其低噪聲特性可避免信號干擾;在航空航天領(lǐng)域,其抗輻射性能確保極端環(huán)境下的可靠性。據(jù)統(tǒng)計,薄膜電阻在工業(yè)控制領(lǐng)域的市場份額正以每年8%的速度增長,凸顯其技術(shù)溢價價值。

技術(shù)演進:互補共生的未來

隨著電子設(shè)備向高密度、高可靠性方向發(fā)展,厚膜與薄膜工藝呈現(xiàn)融合趨勢。例如,厚聲推出的混合工藝電阻,在厚膜基體上沉積薄膜修正層,將精度提升至±0.5%的同時降低成本。而薄膜工藝通過卷對卷(R2R)生產(chǎn)線的引入,使產(chǎn)能提升3倍,逐步縮小與厚膜工藝的成本差距。

兩種工藝的差異化競爭,本質(zhì)是電子行業(yè)對"性價比"與"極致性能"的雙重追求。厚膜工藝以成熟的技術(shù)體系支撐著萬億級電子市場的基礎(chǔ)需求,薄膜工藝則通過持續(xù)創(chuàng)新推動著高端制造的邊界拓展。